An innovation in the form of DDR5 is being actively developed for the use of RAM in various systems. The key characteristic of the project is the use of a logical unit of information stored in a memory bank. It is used in a variety of electronic equipment. Its efficiency depends on the operated devices. The system provides a combination of controller and physical formation of slots.

General description

The full name is Double Data Rate 5 Synchronous Dynamic Random-Access Memory (DDR5 SDRAM). This is a type of synchronous dynamic random-access memory. The standard was released in July 2020. In a standard synchronized program with the SDRAW option, access to operations is guaranteed randomly or at double the information rate.

The DDR5 system consists of many columns and rows containing storage blocks distributed over several chips. In a single write or read version, only one bank is accessed, so the number of bits and chips is equal to the memory bus width (single-channel transfer). The size of the final position depends on the bits in columns and rows multiplied by the number of chips available.

The material described above is quite complex, it requires an experienced approach, yet it is accessible to most users. If the consumer understands that the RAM consists of one or two ranks, he will understand the whole program. Otherwise, experts recommend stopping to consider individual sections.

Dimensions and capacity

The following points can be noted about the size of DDR5 memory:

- Length/height/width – 142/6.5/21.3 mm.

- Tolerance in mm – 133.35/0.15.

- RAM capacity – 133.5 or 133.2 GB.

- Contacts length – 62.9 mm or 57.8 mm.

- Linear transition – 0,5 mm.

The DDR5 system is focused on reducing power consumption on data servers and mobile devices, as well as increasing data throughput. Compared to the previous version, the fifth generation has a 1.35 times more data transfer rate (up to 4800 MT/s).

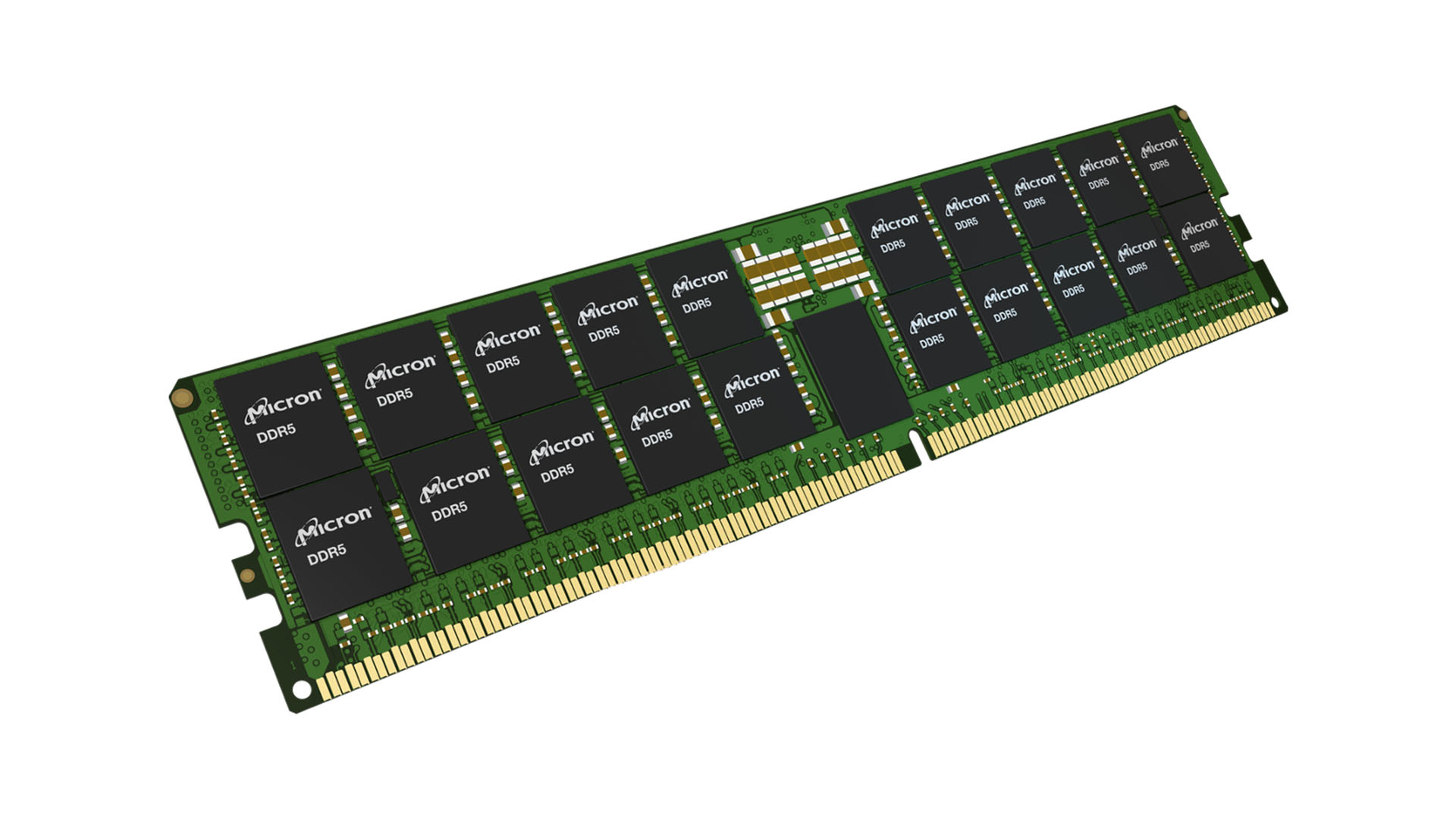

Micron infographics

This metric is tracked across all generations of the program and is constantly being improved. The first version was created back in 2020 for commercial rather than mass use. The efficiency of DDR5 is due to the data transfer speed, capacity, and bandwidth.

Transaction gains between the second and fifth versions increased from 800 to 8400 operations per second. At the same time, the graph of technology development has risen sharply (the lower parameter was 16 GB, the upper – 64 GB).

Throughput per core

The performance of the described program is staggered annually, with frequencies and the number of operations per clock cycle increasing. Maintenance complexity increases, the number of cores increases as well, and the number of manipulations per step stabilizes.

The emergence of DDR5 is due to the fact that memory bandwidth in the IT sphere is growing, and the number of cores is increasing commensurately, but the figure per core, in general, remained at the same level for several years.

In the last couple of years, the skipping ability has even started to drop, so it is already quite uncommon for the CPU performance to be dependent on subsystem memory blocks. All other manipulations are performed as usual with the gradual introduction of new technologies.

Conclusion

Some experts note that there were quite many changes in this sphere. In spite of this, there are concerns about the inflated cost of the program at the beginning of sales on the mass market. Time will dot the i’s, and consumers will have to wait for the out of the product to evaluate its effectiveness and usefulness.